实验一 简单逻辑电路设计与仿真

一、实验目的

1. 学习并掌握CPLD/FPGA实验开发系统的基本操作。

2.学习在MAX+PLUS II 10.2环境下设计简单逻辑电路与功能仿真的方法。

二、实验仪器设备

1. PC机一台。

2. KHF-2型CPLD/FPGA实验开发系统一套。

三、实验要求

1. 预习教材中的相关内容。

2. 阅读并熟悉本次实验的内容。

3. 用图形输入方式完成电路设计。

4. 分析器件的延时特征。

四、实验内容及参考实验步骤

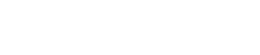

1. 用D触发器设计一个4进制加法器并进行功能仿真。

(1)开机。进入MAX+PLUS II软件系统。

(2)点击File菜单Project子菜单的Name项,出现Project Name对话框。为当前的实验选择恰当的路径并创建项目名称(注意MAX+PLUS II不识别中文路径)。

(3)点击File菜单New项,出现对话框,选择输入方式,这里选择Graphic Editor File。出现图形编辑窗口(注意窗口界面发生了一定变化)。

(4)双击空白编辑区,出现Enter Symbol对话框(或点击Symbol菜单Enter Symbol项)从Symbol Libraries项中选择mf子目录,然后在Symbol File中选择7474元件(双D触发器);在Prim子目录中选择输入脚input和输出引脚output(或者直接在Symbol Name中输入所需元件的名称回车亦可)。

(5)在图形编辑窗口中的左侧点击连线按钮(draws a horizontal or vertical line),并完成对电路的连线(参考电路如图1所示)。

(6)在引脚的PIN_NAME处双击使之变黑,键入引脚名称。

(7)保存文件,使用默认的文件名(与工程文件同名)。

(8)点击File菜单Project子菜单的Set Project to Current File项,使项目名称与当前设计文件相同。

图1 4进制加法计数器

(9)选择器件。点击Assign菜单Device项,选择与下载板主芯片型号统一的器件。(Altera公司的ACEX系列FPGA芯片,EP1K100QC208-3,208引脚,集成度为10万门)

(10)点击File菜单Project子菜单的Save & Check项对文件进行存盘并进行语法检查,然后点击START按钮进行编译。

(11)点击MAX+PLUS II菜单Waveform Editor子菜单出现Waveform Editor窗口。点击Node菜单Enter Nodes From SNF,在Enter Nodes From SNF对话框中点击List按钮、“=>”按钮和OK按钮。并保存波形文件。

(12)点击Options菜单中Grid Size…,打开Grid Size对话框,设置好相应的值。

(13)在Name项下,选择相应的输入端,设定输入波形(可以利用工具栏中的有关按钮)。

(14)点击File菜单Project子菜单的Save & Compile项对文件进行存盘编译。

(15)点击Simulator按钮出现仿真界面。Simulator: Timing Simulator对话框的Start Time和End Time中设定起始和终止时间,点击Start开始仿真。

(16)点击“Open SCF”按钮,观察仿真结果,并进行延时分析,是否与器件标称值相符。

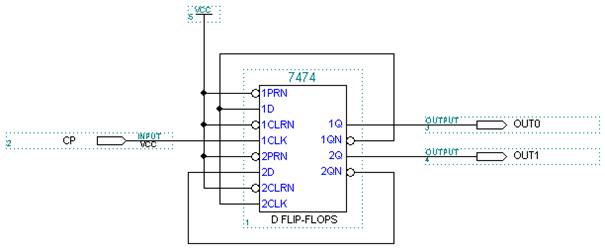

2. 设计一个2-4译码器并进行静态功能仿真。

首先确定2-4译码器的逻辑线路图,如图2所示。

图2 2-4译码器

(1)点击File菜单Project子菜单的Name项建立一个新的项目。

(2)点击New按钮,选择Graphic Editor项新建一个图形输入文件。

(3)双击左键,在Enter Symbol Libraries中双击prim。

(4)在Symbol Files中选用器件。

(5)连线完成电路设计。

(6)双击PIN_NAME键入引脚命名。

(7)保存文件,使用默认的文件名(与工程文件同名)。

(8)点击File菜单Project子菜单的Set Project to Current File项,使项目名称与当前设计文件相同。

(9)选择器件。点击Assign菜单Device项,选择与下载板主芯片型号统一的器件。(Altera公司的ACEX系列FPGA芯片,EP1K100QC208-3,208引脚,集成度为10万门)

(10)点击File菜单Project子菜单的Save & Check项对文件进行存盘并进行语法检查,然后点击START按钮进行编译。

(11)点击MAX+PLUS II菜单Waveform Editor子菜单出现Waveform Editor窗口。点击Node菜单Enter Nodes From SNF,在Enter Nodes From SNF对话框中点击List按钮、“=>”按钮和OK按钮。并保存波形文件。

(12)点击Options菜单中Grid Size…,打开Grid Size对话框,设置好相应的值。

(13)在Name项下,选择相应的输入端,设定输入波形(可以利用工具栏中的有关按钮)。

(14)点击File菜单Project子菜单的Save & Compile项对文件进行存盘编译。

(15)点击Simulator按钮出现仿真界面。Simulator: Timing Simulator对话框的Start Time和End Time中设定起始和终止时间,点击Start开始仿真。

(16)点击“Open SCF”按钮,观察仿真结果,并进行延时分析,是否与器件标称值相符。

五、实验报告

1. 总结用MAX+PLUS II 10.2开发系统对逻辑电路进行设计、仿真的操作步骤。

2. 讨论用CPLD/FPGA开发系统进行逻辑电路设计的特点与优越性。

3. 讨论自己在设计过程中遇到的问题、解决的过程以及收获体会。

实验二 译码与寄存器电路设计与仿真

一、实验目的

1. 掌握CPLD/FPGA实验开发系统的操作技巧。

2.掌握用MAX+PLUS II进行一般数字逻辑电路的设计方法。

3. 学习CPLD/FPGA芯片下载与实验基本方法。

4. 熟悉CPLD/FPGA实验开发系统的基本结构。

5. 掌握使用CPLD/FPGA实验系统的LED显示的方法。

二、实验仪器设备

1. PC机一台。

2. KHF-2型CPLD/FPGA实验开发系统一套。

三、实验要求

1. 预习教材中的相关内容。

2. 阅读并熟悉本次实验的内容。

3. 用图形输入方式完成电路设计。

4. 完成从设计输入到下载的全部设计过程。

5. 学习系统下载软件的界面和使用方法。

四、实验内容及参考实验步骤

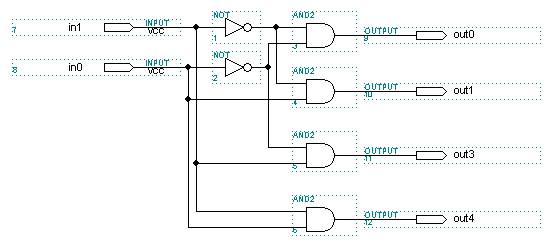

1. 设计一个BCD译码器,进行功能仿真及下载测试。

(1)用图形编辑方法完成电路的输入,以及管脚命名等,具体实验步骤可以参照实验一有关部分,BCD译码器。

图1 BCD译码器

(2)点击File菜单Project子菜单中的“Set Project to Current File”,使得工程文件指定为当前文件。

(3)对文件进行编译。

(4)点击Assign菜单的Device项选择芯片。(Altera公司的ACEX系列FPGA芯片,EP1K100QC208-3)

(5)点击Assign菜单的Pin/Location/Chip项,进行管脚分配。

(6)对电路进行编译。

(7)运行下载软件,选择合适的芯片类型,进行下载。

(8)观察、验证实验电路的正确性。

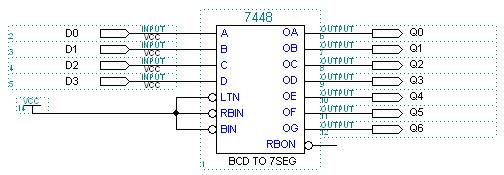

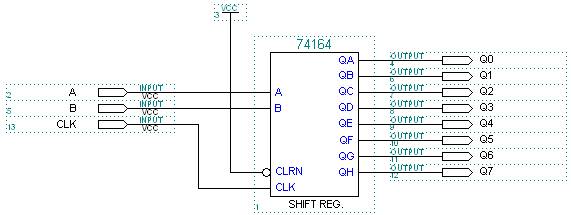

2. 串入并出移位寄存器电路设计、仿真与下载

(1)用图形编辑方法完成电路的输入以及管脚命名等(参考电路如图2所示)。

图2 串入并出移位寄存器

(2)点击File菜单Project子菜单中的“Set Project to Current File”,使得工程文件指定为当前文件。

(3)点击Assign菜单的Device项选择芯片。(Altera公司的ACEX系列FPGA芯片,EP1K100QC208-3)

(4)点击Assign菜单的Pin/Location/Chip项,进行管脚分配。

(5)对电路进行编译。

(6)运行下载软件,选择合适的芯片类型,进行下载。

(7)观察、验证实验电路的正确性。

五、实验报告

1. 总结进行CPLD/FPGA电路设计与仿真的操作步骤和技巧。

2. 讨论在设计与实验过程中遇到的问题、解决的办法及收获。

7448:BCD7段显示译码器

LTN |

RBIN |

BIN |

D |

C |

B |

A |

OA |

OB |

OC |

OD |

OE |

OF |

OG |

RBON |

功能 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

X |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

X |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

2 |

1 |

X |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

3 |

1 |

X |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

4 |

1 |

X |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

5 |

1 |

X |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

6 |

1 |

X |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

7 |

1 |

X |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

8 |

1 |

X |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

9 |

1 |

X |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

|

1 |

X |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

|

1 |

X |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

|

1 |

X |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

|

1 |

X |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

|

1 |

X |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

|

X |

X |

0 |

X |

X |

X |

X |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

熄灭输入 |

1 |

0 |

X |

L |

L |

L |

L |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

动态灭零 |

0 |

X |

X |

X |

X |

X |

X |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

试灯 |

74164:串入并出移位寄存器

CLK |

CLRN |

A |

B |

QA QB … QH |

X |

0 |

X |

X |

0 0 … 0 |

0 |

1 |

X |

X |

QA0 QB0 QH0.. |

上升沿 |

1 |

1 |

1 |

1 QAn QGn |

上升沿 |

1 |

0 |

X |

0 QAn QGn |

上升沿 |

1 |

X |

0 |

0 QAn QGn |

|

|

|

|

|

实验三 全加器设计、仿真与下载

一、实验目的

1. 熟练掌握MAX+PLUS II的使用。

2. 掌握一位全加器的设计方法、学会用一位全加器组成四位全加器。

3. 掌握CPLD/FPAG开发系统硬件电路的下载及测试。

4. 学习模块化电路设计方法。

二、实验仪器设备

1. PC机一台。

2. KHF-2型CPLD/FPGA实验开发系统一套。

三、实验要求

1. 预习组合逻辑电路中一位、四位全加器的设计方法。

2. 预习CPLD/FPGA开发系统(硬件电路)中的开关及发光管的使用方法。

3. 预习本次实验内容。

4. 用图形编辑方法输入电路。

四、实验内容及参考实验步骤

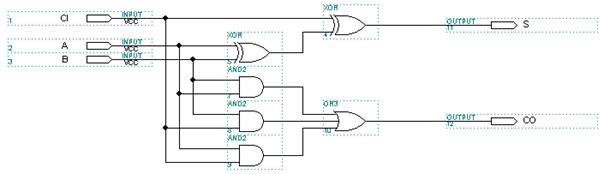

1. 设计一位全加器

(1)完成电路的输入,以及对引脚的命名等(参考电路如图1所示)

图1 一位全加器

(2)对一位全加器进行编译、仿真和下载。(注意:这时PC机应与实验通过串口线相联。)

(3)点击File菜单的Create Default Symbol项,创建缺省模块。

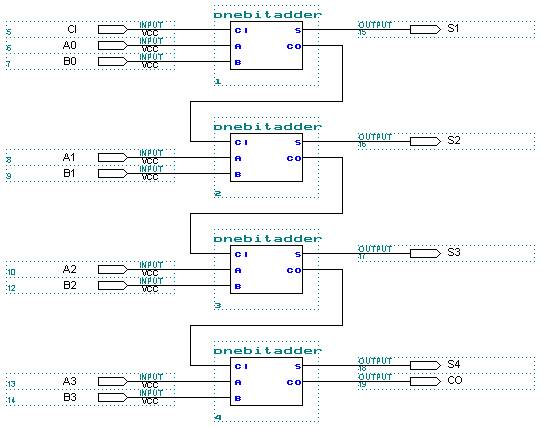

2. 利用一位全加器模块进行四位全加器的设计

(1)新建一个图形设计文件,在图形编辑区内双击左键,从Enter Symbol对话框中的用户目录(自建目录)下选择上面所创建的模块名。

(2)连接线路,并进行编译(如图2所示)。

(3)点击Assign菜单的Device项选择芯片。(Altera公司的ACEX系列FPGA芯片,EP1K100QC208-3)

(4)管脚分配。(根据实验箱中资源设置进行管脚的分配)

(5)编译,并进行下载。

(6)观察实验结果。

图2 四位全加器

五、实验报告

1. 总结模块化电路设计的方法。

2. 总结用MAX+PLUS II进行电路设计的实质。

3. 总结用MAX+PLUS II进行电路设计的一般步骤。

实验四 利用硬件描述语言进行数字钟设计

一、实验目的

1. 进一步学习用硬件描述语言进行电路设计的方法。

2. 初步掌握较复杂电路的设计方法。

二、实验仪器设备

1. PC机一台。

2. KHF-2型CPLD/FPGA实验开发系统一套。

三、实验要求

1. 预习实验内容。

2. 用硬件描述语言(VHDL)设计60进制的数字钟。(可以在此基础上设计更为复杂的一个带有小时、分、秒的数字钟)。

3. 用数码管显示结果。

四、参考程序

VHDL语言描述的60归0的参考程序

library IEEE; -----调用库

use IEEE.std_logic_1164.all;

use IEEE.std_logic_unsigned.all;

entity count60 is port ----实体描述

( inclk: in STD_LOGIC; ----端口说明

outa: out STD_LOGIC_VECTOR (6 downto 0);

outb: out STD_LOGIC_VECTOR (6 downto 0));

end count60;

architecture count60_arch of count60 is ----结构体描述

signal ma, mb: std_logic_vector(3 downto 0);

signal f: std_logic;

signal md: std_logic_vector (23 downto 0);

begin

P1: process(inclk) ----分频进程模块

begin

if inclk' event and inclk='1' then

if md = 4999999 then

md <= "000000000000000000000000";

f <= not f;

else

md <= md + 1;

f <= f;

end if;

end if;

end process P1;

P2: process(f) ----60归0进程模块

begin

if f'event and f='1' then

if ma=9 then

ma <= "0000";

if mb=5 then

mb <= "0000";

else

mb <= mb + 1;

end if;

else

ma <= ma + 1;

end if;

end if;

end process P2;

with ma select ----段码转换模块

outa <= "0110000" when "0001", --1

"1101101" when "0010", --2

"1111001" when "0011", --3

"0110011" when "0100", --4

"1011011" when "0101", --5

"1011111" when "0110", --6

"1110000" when "0111", --7

"1111111" when "1000", --8

"1111011" when "1001", --9

"1110111" when "1010", --A

"0011111" when "1011", --B

"1001110" when "1100", --C

"0111101" when "1101", --D

"1001111" when "1110", --E

"1000111" when "1111", --F

"1111110" when others; --0

with mb select ----段码转换模块

outb <= "0110000" when "0001", --1

"1101101" when "0010", --2

"1111001" when "0011", --3

"0110011" when "0100", --4

"1011011" when "0101", --5

"1011111" when "0110", --6

"1110000" when "0111", --7

"1111111" when "1000", --8

"1111011" when "1001", --9

"1110111" when "1010", --A

"0011111" when "1011", --B

"1001110" when "1100", --C

"0111101" when "1101", --D

"1001111" when "1110", --E

"1000111" when "1111", --F

"1111110" when others; --0

end count60_arch;

五、实验报告

1、总结并体会初步设计稍大规模电路的基本思路和方法。

2、根据实验中遇到的问题及实验结果写出总结报告。

实验五 BCD码转换电路设计

一、实验目的

1. 用硬件描述语言设计较复杂电路。

2. 掌握综合性电路的设计方法。

二、实验仪器设备

1. PC机一台。

2. KHF-2型CPLD/FPGA实验开发系统一套。

三、实验要求

1. 复习BCD码转换的原理。

2. 复习教材相关内容。

3. 用硬件描述语言进行电路设计。

四、实验内容及参考实验步骤

BCD码转换电路VHDL程序示例

library ieee; --调用库

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity bcdconvert is

port ( ina: in std_logic_vector (7 downto 0);

inclk: in std_logic;

outa: out std_logic_vector (6 downto 0);

outb: out std_logic_vector (6 downto 0);

outc: out std_logic_vector (6 downto 0)

);

end bcdconvert;

architecture arch_bcdconvert of bcdconvert is --结构体说明

signal sina: std_logic_vector (7 downto 0); --信号定义

signal souta: std_logic_vector (3 downto 0);

signal soutb: std_logic_vector (3 downto 0);

signal soutc: std_logic_vector (3 downto 0);

signal ssouta: std_logic_vector (3 downto 0);

signal ssoutb: std_logic_vector (3 downto 0);

signal ssoutc: std_logic_vector (3 downto 0);

begin

process(inclk) --隐含状态机的使用

begin

if (inclk'event and inclk='1') then

if sina="0000000" then

ssouta <= souta;

ssoutb <= soutb;

ssoutc <= soutc;

souta <= "0000";

soutb <= "0000";

soutc <= "0000";

sina <= ina;

else

sina <= sina - 1;

if souta = 9 then

souta <= "0000";

if soutb = 9 then

soutb <= "0000";

soutc <= soutc + 1;

else

soutb <= soutb + 1;

end if;

else

souta <= souta + 1;

end if;

end if;

end if;

end process;

with ssouta select --段码转换模块

outa <= "0110000" when "0001",

"1101101" when "0010",

"1111001" when "0011",

"0110011" when "0100",

"1011011" when "0101",

"1011111" when "0110",

"1110000" when "0111",

"1111111" when "1000",

"1111011" when "1001",

"1110111" when "1010",

"0011111" when "1011",

"1001110" when "1100",

"0111101" when "1101",

"1001111" when "1110",

"1000111" when "1111",

"1111110" when others;

with ssoutb select --段码转换模块

outb <= "0110000" when "0001",

"1101101" when "0010",

"1111001" when "0011",

"0110011" when "0100",

"1011011" when "0101",

"1011111" when "0110",

"1110000" when "0111",

"1111111" when "1000",

"1111011" when "1001",

"1110111" when "1010",

"0011111" when "1011",

"1001110" when "1100",

"0111101" when "1101",

"1001111" when "1110",

"1000111" when "1111",

"1111110" when others;

with ssoutc select --段码转换模块

outc <= "0110000" when "0001",

"1101101" when "0010",

"1111001" when "0011",

"0110011" when "0100",

"1011011" when "0101",

"1011111" when "0110",

"1110000" when "0111",

"1111111" when "1000",

"1111011" when "1001",

"1110111" when "1010",

"0011111" when "1011",

"1001110" when "1100",

"0111101" when "1101",

"1001111" when "1110",

"1000111" when "1111",

"1111110" when others;

end arch_bcdconvert;

程序简单说明:由于KHF-2型实验系统中,并行显示的数码管只有两个,而本实验中使用三个,因此需要用一个串扫的数码管,考虑到Altera的CPLD/FPGA芯片在没有使用的I/O输出为高电平,因此只要定义一个扫描脚如selbit(可以锁定到P170)并置为GND即可。

VHDL语言应为:

selbit: out std_logic_vector(2 downto 0);

逻辑值为:

selbit <="000" (实验中这里应该设置为"111",因为试验箱上共阴极有一个反相器,经过反相器就为"000"了)

五、实验报告

1. 总结设计复杂程序的方法。

2. 总结在程序设计中的算法。

3. 写出实验总结报告。

实验六 数据采集与显示电路设计

一、实验目的

1. 学会用硬件描述语言设计A/D转换电路。

2. 掌握综合性电路的设计方法。

二、实验仪器设备

1. PC机一台。

2. KHF-2型CPLD/FPGA实验开发系统一套。

三、实验要求

1. 复习A/D转换电路的原理(熟悉ADC0809芯片原理及使用方法)。

2. 复习教材相关内容。

3. 用硬件描述语言进行电路设计。

四、实验内容及参考实验步骤

1. 用VHDL编写实例

library ieee; --调用库

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity adc0809 is --实体说明

port ( ina: in std_logic_vector(7 downto 0); --定义输入输出

inclk: in std_logic;

eoc: in std_logic;

outa: out std_logic_vector(13 downto 0);

adda, addb, addc: out std_logic;

ck, ale: out std_logic);

end adc0809;

architecture arch_adc0809 of adc0809 is --结构体说明

signal fp: std_logic_vector(2 downto 0); --信号定义

signal f: std_logic;

signal counter: std_logic_vector(3 downto 0);

signal sa: std_logic_vector(7 downto 0);

begin

process(inclk) --进程说明,分频模块

begin

if (inclk'event and inclk='1') then

if fp=5 then

fp<="000";

f<=not f;

else

fp<=fp+1;

end if;

end if;

end process;

ck<=f;

process(f) --数据传递

begin

if (f'event and f='1') then

if counter=8 then

counter<="0000";

sa<=ina;

else counter<=counter + 1;

end if;

end if;

end process;

ale<=eoc; --A/D转换结果允许输出控制

adda<='0';

addb<='0';

addc<='0';

with sa (3 downto 0) select --段码转换模块

outa(6 downto 0)<="0110000" when "0001",

"1101101" when "0010",

"1111001" when "0011",

"0110011" when "0100",

"1011011" when "0101",

"1011111" when "0110",

"1110000" when "0111",

"1111111" when "1000",

"1111011" when "1001",

"1110111" when "1010",

"0011111" when "1011",

"1001110" when "1100",

"0111101" when "1101",

"1001111" when "1110",

"1000111" when "1111",

"1111110" when others;

with sa(7 downto 4) select

outa(13 downto 7)<="011000" when "0001",

"1101101" when "0010",

"1111001" when "0011",

"0110011" when "0100",

"1011011" when "0101",

"1011111" when "0110",

"1110000" when "0111",

"1111111" when "1000",

"1111011" when "1001",

"1110111" when "1010",

"0011111" when "1011",

"1001110" when "1100",

"0111101" when "1101",

"1001111" when "1110",

"1000111" when "1111",

"1111110" when others;

end arch_adc0809;

2. 编译。

3. 管脚分配

4. 后编译、下载。

五、实验报告

1. 画出adc0809的时序图。

2. 了解CPLD在工业监控中的应用。

3. 写出本次实验的实验报告